【最新発明情報】スナバ回路不要のサージ抑制型電力変換システム

解析的な設計が容易なサージ抑制方法を、スナバ回路などのサージ抑制付加回路無しで実現する電力変換システムです。

背景

近年、SiCやGaN等のワイドギャップ半導体の実用化により、従来の電力変換器に比べより高周波および大電力でのスイッチングが可能となりました。これにより、電力変換器の小型化、軽量化が進められています。

その一方、これら高周波スイッチングに伴う電圧変化や電流変化が増大することにより、スイッチング時の電圧サージという課題が、より顕在化しています。

この対策として、サージ抑制用の付加回路増設という方法がありますが、これは変換器体積の増加とコストアップにつながってしまいます。

発明概要と利点

発明者らは、スナバ回路などのサージ抑制付加回路を要さない、新たなサージ抑制手法を開発しました。本手法では、予め回路定数計算にて電流がゼロとなる時間を求めることで、パルス密度変調(PDM)のオフとなる時間を他励で制御するため、電力変換器としての解析的な設計が容易であり、また、サージ検知抑制用に付加回路を増設する必要がありません。

- 付加回路無し

サージ抑制の付加回路が不要なため、ワイドギャップ半導体による電力変換器の小型化、軽量化とコストダウン化に適します。また付加回路によるスイッチング損失増大の可能性もありません。

- ターンオフ時のサージ抑制

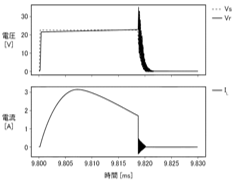

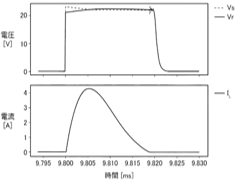

本発明手法を用いることで、スイッチング時に発生していたサージを抑制することができます (図1(A)(B)) 。

- 設計済みの回路に対しても実装可能

振動成分によって電流が0をとる時間を予め回路定数計算可能な設計済みの回路に対して制御のみで本発明手法を実装することができます。

(A)発明手法なし

(B)発明手法あり

図1.本発明によるサージ抑制効果評価試験

DCーDCコンバータ回路に、発明手法なしの場合(A)に発生したスイッチターンオフ時のサージ電圧が、発明手法を用いた場合(B)にはゼロに近く効果的に抑制されました。

研究段階

本発明を用いた回路シミュレーションにおいて、サージ抑制用回路の増設無しに、電圧(送電側・受電側)及び電流を測定し、サージ抑制を確認済み。

適応分野

- DC-DCコンバータにおける装置の大容量化かつ小型化

- DC/DC電源制御用IC

- パケット送電ルータ

希望の連携形態

- 実施許諾契約*

- オプション契約*

*京都大学より特許出願中(未公開)です。

ライセンス契約を受けていただき 本発明の実用化を目指していただける企業様を募集しています。ぜひ、お問い合わせください。

高周波半導体素子の開発が進むに伴い課題となっている、スイッチングで起こる電圧サージを簡単にコントロール可能とする技術です!

京都大学産学連携担当(株式会社TLO京都)担当:藤田 直子より